н•ҷмӮ¬н–үм •

н•ҷкіјкіөм§ҖмӮ¬н•ӯ

[кіөм§Җ] кІҪкё°лҸ„мқјмһҗлҰ¬мһ¬лӢЁ л°ҳлҸ„мІҙм„Өкі„ көҗмңЎкіјм • м•ҲлӮҙ

- кҙҖлҰ¬мһҗ

- 2020-05-18

- 1627

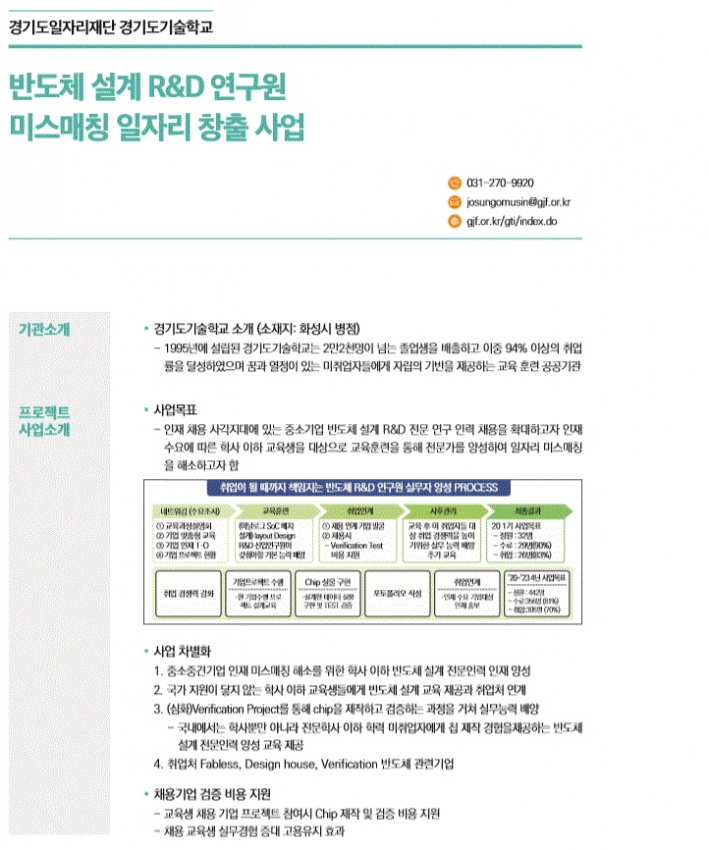

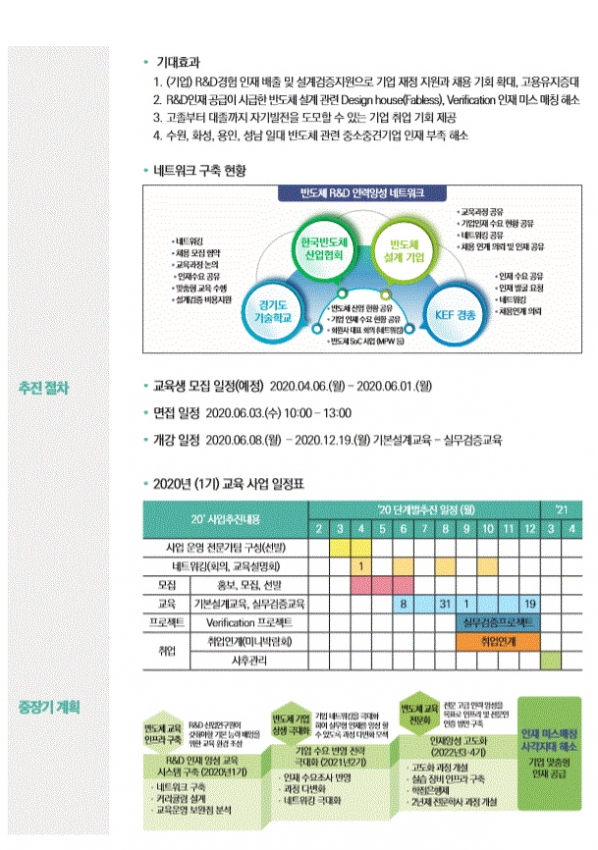

в—Ҷ мӮ¬м—… : л°ҳлҸ„мІҙ м„Өкі„ R&D м—°кө¬мӣҗ лҜёмҠӨл§Өм№ӯ мқјмһҗлҰ¬ м°Ҫм¶ң мӮ¬м—…

в—Ҷ м§Җм—ӯмӮ°м—…л§һм¶Ө нҳҒмӢ н”„лЎңм қнҠё

кіјм •лӘ…: SoC Analog mixed Design (layout Design)

көҗмңЎкө¬л¶„ | м·Ём—…м—°кі„көҗмңЎ | кіјм •лӘ… | SoC Analog mixed Design | ||||||||||||||||

м„ёл¶Җкіјм • | кё°ліём„Өкі„көҗмңЎ ; (м•„лӮ лЎңк·ё SoC л°°м№ҳ м„Өкі„) layout Design мӢӨл¬ҙкІҖмҰқкөҗмңЎ : (мӢ¬нҷ”)Verification Project | ||||||||||||||||||

мҲҳк°•мӢ мІӯкё°к°„ | 2020.04.13.(мӣ”) ~ 2020.06.01.(18мӢң к№Ңм§Җ) | л©ҙм ‘мқј | 2020.06.03.(мҲҳ)/ 10~13мӢң | ||||||||||||||||

м§ҖмӣҗмһҗкІ© | o лҜём·Ём—… мІӯл…„ л°Ҹ кІҪл Ҙ ліҙмң мһҗ(кІҪл ҘлӢЁм Ҳ), л§Ң18~40м„ё (кө°н•„) лҢҖмғҒ o н•ҷл Ҙл¬ҙкҙҖ (м „кіө кҙҖл Ёмһҗ мҡ°лҢҖ м„ л°ң/ л°ҳлҸ„мІҙ, м „мһҗ, нҶөмӢ , м „кё°) o м·Ём•Ҫкі„мёөмқ„ л°°л Өн•ң көҗмңЎмғқ м •мӣҗмқҳ 10% мҡ°м„ м„ л°ң | ||||||||||||||||||

мҲҳк°•мӢ мІӯ л°Ҹ м ңм¶ңм„ңлҘҳ | o кІҪкё°лҸ„кё°мҲ н•ҷкөҗ нҷҲнҺҳмқҙм§Җ (www.gjf.or.kr/gti.index.do) o кіјм •мҶҢк°ң көҗмңЎкіјм •м•ҲлӮҙ > м§Җм—ӯмӮ°м—…л§һм¶Өнҳ• көҗмңЎкіјм • > л°ҳлҸ„мІҙм„Өкі„R&Dмқёмһ¬м–‘м„ұкіјм • o мҲҳк°•мӢ мІӯ көҗмңЎм ‘мҲҳ > м§Җм—ӯмӮ°м—…л§һм¶Өнҳ• көҗмңЎкіјм • > л°ҳлҸ„мІҙм„Өкі„R&Dмқёмһ¬м–‘м„ұкіјм • o м ңм¶ңм„ңлҘҳ - н•ҷл ҘмҰқлӘ…м„ң / нҶ мқөм„ұм Ғ / м„ұм ҒмҰқлӘ…м„ң / мҲҳмғҒмӢӨм Ғ / л…јл¬ёмӢӨм Ғ л“ұ | ||||||||||||||||||

көҗмңЎкё°к°„ | o 1м°Ё кё°ліём„Өкі„көҗмңЎ 2020.06.08.~2020.08.31. o 2м°Ё мӢӨл¬ҙкІҖмҰқкөҗмңЎ 2020.09.01.~2020.12.19. | мӢңк°„ | мЈј 6мқј (мқј ? кёҲ) 09:00 ~ 18:00 | ||||||||||||||||

к°•мӮ¬лӘ… | мөңмһ¬мҡ© көҗмҲҳ мҷё 4лӘ… | көҗмңЎл№„ | м „м•Ў л¬ҙлЈҢ | ||||||||||||||||

мһҘмҶҢ | кІҪкё°лҸ„кё°мҲ н•ҷкөҗ м»ҙн“Ён„°мӢңмҠӨн…ңкҙҖ 1мёө л°ҳлҸ„мІҙ к°•мқҳмһҘ | м •мӣҗ | 32лӘ… | ||||||||||||||||

көҗмңЎлӘ©н‘ң л°Ҹ к°ңмҡ” | 1. көҗмңЎлӘ©н‘ң Fabless л°Ҹ Design house л°ҳлҸ„мІҙ м„Өкі„ R&D м „л¬ё м—°кө¬мӣҗмқ„ м–‘м„ұн•ҳкё° мң„н•ҙ мӢ мһ… м—°кө¬мӣҗмқҙ кё°м—…м—җм„ң мІҳмқҢ 진н–үн•ҳлҠ” м„Өкі„м—…л¬ҙмқё layout desgnл¶Җн„° Analog м„Өкі„к№Ңм§Җ мқҙлЎ кіј мӢӨмҠөмқ„ лі‘н–үн•ҳм—¬ л°ҳлҸ„мІҙ м„Өкі„ м—°кө¬мӣҗмқ„ м–‘м„ұн•Ё 2. к°ңмҡ” 3. көҗмңЎ лӮҙмҡ©

| ||||||||||||||||||

көҗмңЎл°©лІ• | o мқҙлЎ л°Ҹ мӢӨмҠө, н”„лЎңм қнҠё | ||||||||||||||||||

м„ мҲҳн•ҷмҠө | o м„ мҲҳн•ҷмҠө - л””м§Җн„ё л…јлҰ¬нҡҢлЎң, нҡҢлЎңмқҙлЎ , м „мһҗнҡҢлЎң, Cм–ём–ҙ, лҰ¬лҲ…мҠӨOS мҷҖ viм—җл””н„° л“ұ | ||||||||||||||||||

нҠ№мқҙмӮ¬н•ӯ | o мҲҳлӢ№: м¶ңм„қ 80% мқҙмғҒ 20л§Ңмӣҗ м§Җкёү o нҶөн•ҷлІ„мҠӨ мҡҙмҳҒ(л§қнҸ¬м—ӯ, лі‘м җм—ӯ, мҲҳмӣҗл…ём„ ) o кё°мҲҷмӮ¬ мҡҙмҳҒ(л¬ҙлЈҢ / нҶөн•ҷ лЁј кұ°лҰ¬ мҲң л°°м •) o кө¬лӮҙмӢқлӢ№ мҡҙмҳҒ : 1мқј 3мӢқ(л¬ҙлЈҢ), нҶ мҡ”мқј мЎ°мӢқ, мӨ‘мӢқ м ңкіө | ||||||||||||||||||

л¬ёмқҳ | o кІҪкё°лҸ„кё°мҲ н•ҷкөҗ көҗмңЎм§ҖмӣҗнҢҖ 031-270-9920 | ||||||||||||||||||